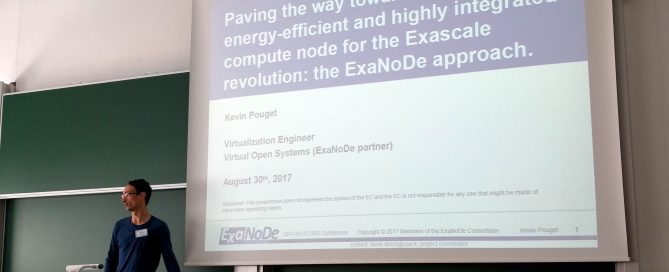

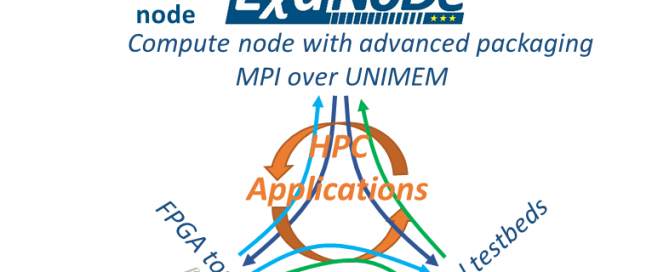

Press release: ExaNode project produced groundbreaking compute unit prototype for Exascale

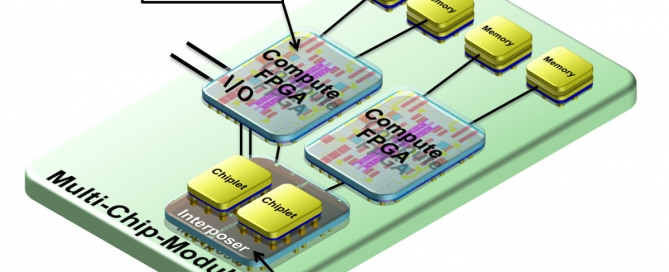

The ExaNode Project finished successfully in summer 2019 The project has built a groundbreaking compute unit prototype paving the way to tomorrow’s exascale supercomputers, those capable of performing a billion billion calculations per second, or ten times faster than today’s most powerful computers. Read more in our general and technical press releases: Press release – with technical details (PDF) Press release – for the general public (PDF)