# D3.2

Runtime systems (OmpSs, OpenStream) and communication libraries (GPI, MPI): Advanced implementation customized for ExaNoDe architecture, interconnect, operating system

| Workpackage:  | 3 Enablement of Software Compute Node |                    |                  |  |

|---------------|---------------------------------------|--------------------|------------------|--|

| Author(s):    | Valeria Barts                         | sch, Carsten       | FHG              |  |

|               | Lojewski                              |                    |                  |  |

|               | Antoniu Pop                           |                    | UOM              |  |

|               | Paul Carpent                          | er, Babis Chalios, | BSC              |  |

|               | Antonio J. Pe                         | eña, Kyunghun Kim  |                  |  |

|               | Andrea Barto                          | olini, Francesco   | ETHZ             |  |

|               | Conti                                 |                    |                  |  |

| Authorized by | Paul Carpent                          | er                 | BSC              |  |

| Reviewer      | Paul Carpent                          | er                 | BSC              |  |

| Reviewer      | Giuliano Taf                          | foni               | INAF (ExaNeSt    |  |

|               |                                       |                    | WP2 Applications |  |

|               | lead)                                 |                    |                  |  |

| Reviewer      | Manolis Mar                           | FORTH              |                  |  |

| Dissemination | Dublic (DII)                          |                    |                  |  |

| Level         | Public (PU)                           |                    |                  |  |

| Date       | Author         | Comments                       | Version | Status |

|------------|----------------|--------------------------------|---------|--------|

| 2017-07-18 | Antonio Pena   | Initial MPI Version added      | V0.1    | Draft  |

| 2017-07-21 | Carsten        | GPI Version added              | V0.2    | Draft  |

|            | Lojewski       |                                |         |        |

| 2017-08-28 | Babis Chalios, | OmpSs, OpenStream and parallel | V0.3    | Draft  |

|            | Antonio Pop    | runtime support section added  |         |        |

| 2017-08-30 | Antonio Pena   | Updated MPI version, including | V0.4    | Draft  |

|            |                | measurements                   |         |        |

| 2017-08-31 | Andrea           | Power Management added             | V0.5 | Draft     |

|------------|------------------|------------------------------------|------|-----------|

|            | Bartolini        |                                    |      |           |

| 2017-09-06 | Valeria Bartsch  | Executive Summary, Introduction,   | V0.6 | Final     |

|            |                  | Concluding Remarks added           |      |           |

| 2017-09-26 | Paul Carpenter,  | Reviewer's comment and suggestions | V0.7 | Including |

|            | Giuliano         | added                              |      | some of   |

|            | Taffoni,         |                                    |      | the       |

|            | Manolis          |                                    |      | reviewers |

|            | Marazakis,       |                                    |      | comments  |

|            | Antoniu Pop,     |                                    |      |           |

|            | Valeria Bartsch, |                                    |      |           |

|            | Paul Carpenter,  |                                    |      |           |

|            | Antonio Pena,    |                                    |      |           |

|            | Andrea           |                                    |      |           |

|            | Bartolini        |                                    |      |           |

# **Executive Summary**

In this deliverable, we describe the runtime systems (OmpSs and OpenStream) and communication libraries (GPI and MPI) being adapted to the ExaNoDe hardware. These runtime systems and libraries will provide standard and portable programming interfaces so that an application can take advantage of the unique system characteristics of the ExaNoDe prototype without needing to optimize the application for the specific UNIMEM APIs defined in D3.6 [1] and D3.7 [2].

All runtime systems and communication library have started to integrate UNIMEM which provides non-coherent load-store and RDMA access to any other remote node. The integration with UNIMEM will allow applications to transparently benefit from UNIMEM using the abovementioned runtimes and communication libraries. OpenStream, MPI and GPI are being directly coupled with the UNIMEM API, while OmpSs uses the underlying MPI layer to indirectly couple with UNIMEM. To ease the integration effort an emulation library is being used allowing tests on a standard x86\_64 SMP system without the need to have the prototype hardware available on site. Tests using the emulation library have been successful. In the third year the partners plan to use ARM+FPGA prototypes to test their system integration.

The following limitations of the UNIMEM library have been found when customizing the implementations to UNIMEM and are under discussion with FORTH:

- Cooperation between FORTH and the other partners (particularly FHG) resulted in an extension to the UNIMEM API functionality. Until July 2017, the prototypes had a bug when using more than one buffer allocation registered with the communication hardware, and no memory registration API was not available. There was also an issue that the UNIMEM API incorrectly specified that only one buffer could be registered at a time. This prevented registering user-provided memory buffers preventing in turn a low-latency zero-copy approach. This bottleneck should now be resolved in the newest UNIMEM software and needs to be tested.

- A parallel startup mechanism like mpi\_run or gpi\_run is not yet available and standard tools and scripts cannot be used on UNIMEM. In addition, environment settings/variables and command line arguments must be communicated to the remote node and setup correctly before a process inside a parallel topology can start. We are in the process of defining an interface that fulfils the requirements for GPI and MPI to start up remote processes.

In addition to the integration with UNIMEM all runtime systems and communication libraries also start to integrate FPGA support e.g. based on experience from previous projects. E.g. BSC has participated in the AXIOM project, UoM is participating in the EcoSCALE project.

Finally, this deliverable describes other runtime support, specifically regarding thermal and power management and runtime libraries for performance-critical primitives:

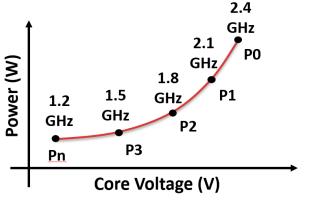

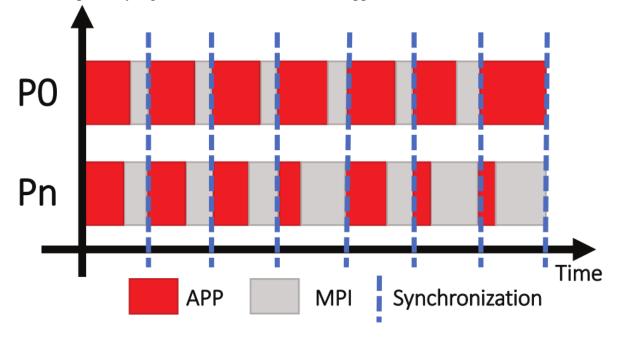

- The ExaNoDe hardware does not provide hardware mechanisms to control power consumption, so the power and thermal control in the scope of the project will directly control the frequency of cores to optimise the power reduction while minimizing the application performance loss. With the MPI profiling tool in the reference application QuantumESPRESSO a DVFS (Dynamic Voltage Frequency Scaling) based power capping approach has been tested and has shown competitive results with respect to hardware based power and thermal control mechanisms.

- Dynamic load balancing has been implemented as a dynamic load balancing library on top of UNIMEM. It relies on remote atomic operations provided by UNIMEM for which an emulation library has been developed which is integrated with the FORTH RDMA emulation library.

These technologies will be made available and potentially integrated into the optimized implementations of GPI, OmpSs, OpenStream and MPI.

# **Table of Contents**

| 1                        |                                      |                                             | ion                                                                        |    |  |  |  |

|--------------------------|--------------------------------------|---------------------------------------------|----------------------------------------------------------------------------|----|--|--|--|

| 2                        | *j~*                                 |                                             |                                                                            |    |  |  |  |

|                          | 2.1                                  | Om                                          | pSs                                                                        |    |  |  |  |

|                          | 2.1.                                 | 1                                           | Introduction to OmpSs-v2                                                   | 3  |  |  |  |

|                          | 2.1.                                 | Nanos6 runtime system on distributed memory | 4                                                                          |    |  |  |  |

|                          | 2.2                                  | •                                           |                                                                            |    |  |  |  |

|                          | 2.2.                                 | -                                           | Introduction to OpenStream                                                 |    |  |  |  |

|                          | 2.2.                                 | 2                                           | Exploiting UNIMEM in OpenStream                                            |    |  |  |  |

|                          | 2.2.                                 | Implementation                              |                                                                            |    |  |  |  |

|                          |                                      | 2.2.4 ExaNode Mini-app                      |                                                                            |    |  |  |  |

|                          | 2.2.                                 |                                             | Towards FPGA integration                                                   |    |  |  |  |

|                          |                                      |                                             | Illel runtime support                                                      |    |  |  |  |

|                          | 2.3.                                 |                                             | Introduction                                                               |    |  |  |  |

|                          | 2.3.                                 |                                             | Optimized runtime support                                                  |    |  |  |  |

| 3                        |                                      |                                             | ication Libraries                                                          |    |  |  |  |

| 5                        | 3.1                                  |                                             |                                                                            |    |  |  |  |

|                          | 3.1                                  |                                             | Introduction to GPI                                                        |    |  |  |  |

|                          | 3.1.                                 |                                             | Exploiting UNIMEM in GPI                                                   |    |  |  |  |

|                          | 3.1.                                 |                                             | ı ç                                                                        |    |  |  |  |

|                          |                                      | -                                           | Design of preliminary software implementation                              |    |  |  |  |

|                          | 3.1.                                 |                                             | Suitable ExaNode Mini-app                                                  |    |  |  |  |

|                          | 3.1.5 Current Status and Limitations |                                             |                                                                            |    |  |  |  |

|                          | 3.1.                                 |                                             | FPGA Prototype System                                                      |    |  |  |  |

|                          |                                      |                                             |                                                                            |    |  |  |  |

|                          | 3.2.                                 |                                             | State-of-the-Art MPICH                                                     |    |  |  |  |

|                          | 3.2.                                 |                                             | MPI over UNIMEM Architecture                                               |    |  |  |  |

|                          | 3.2.                                 |                                             | Development Approach and Current Status                                    |    |  |  |  |

|                          | 3.2.                                 |                                             | Preliminary results                                                        |    |  |  |  |

|                          |                                      |                                             | her Requirements of the runtimes and communication models on the underlyin |    |  |  |  |

|                          | -                                    |                                             |                                                                            |    |  |  |  |

|                          | 3.3.                                 |                                             | Requirements of OmpSs                                                      |    |  |  |  |

|                          | 3.3.                                 |                                             | Requirements of OpenStream                                                 |    |  |  |  |

|                          | 3.3.                                 |                                             | Requirements of GPI                                                        |    |  |  |  |

|                          | 3.3.                                 |                                             | Requirements of MPI                                                        |    |  |  |  |

|                          | 3.4                                  |                                             | able ExaNoDe Mini-apps                                                     |    |  |  |  |

| 4                        |                                      | Power and thermal control                   |                                                                            |    |  |  |  |

|                          | 4.1                                  | HPC                                         | C Architectures                                                            | 24 |  |  |  |

|                          | 4.2                                  | Pow                                         | ver Management in HPC Systems                                              | 25 |  |  |  |

|                          | 4.3                                  | Har                                         | dware Power Controller                                                     | 26 |  |  |  |

|                          | 4.4                                  | Arc                                         | hitecture Target                                                           | 27 |  |  |  |

|                          | 4.5                                  | Moi                                         | nitoring Runtime                                                           | 27 |  |  |  |

|                          | 4.6                                  | .6 Methodology                              |                                                                            |    |  |  |  |

| 4.7 System Analysis      |                                      |                                             | tem Analysis                                                               | 29 |  |  |  |

| 4.8 Application Analysis |                                      |                                             |                                                                            | 30 |  |  |  |

|                          | 4.9                                  |                                             | act on the power and thermal runtime support                               |    |  |  |  |

| 5                        | Conc                                 | -                                           | ng Remarks                                                                 |    |  |  |  |

| 6                        |                                      |                                             | ork                                                                        |    |  |  |  |

| 7                        | Refe                                 | rence                                       | es and Applicable Documents                                                | 36 |  |  |  |

# **Table of Figures**

| Figure 1: Fine-grained release of dependencies using the weakwait construct of OmpSs-v2.        | 3    |

|-------------------------------------------------------------------------------------------------|------|

| Figure 2: Virtual Memory (VM) address space representation of cluster nodes managed by          |      |

| Nanos6                                                                                          | 5    |

| Figure 3: Distributed allocation in Nanos6 is a collective operation. The array is allocated fi | irst |

| on all nodes and then logically distributed across them                                         | 6    |

| Figure 4: Nanos6 task offloading. A ready task can be offloaded to a remote node. All tasks     | \$   |

| with a dependency on the offloaded task will wait until the offloaded signals its               |      |

| completion                                                                                      | 7    |

| Figure 5: Scaling of a matrix vector multiplication operation implemented in OmpSs with         |      |

| Nanos6 Clusters                                                                                 | 8    |

| Figure 6: Scaling of a matrix vector multiplication operation implemented in MPI                |      |

| Figure 5: GPI Building blocks for ExaNoDe architecture support                                  | . 13 |

| Figure 6: GPI Building Blocks of UNIMEM                                                         |      |

| Figure 7: GPI-2 bandwidth on UNIMEM Prototype system (Sockets over Unimem)                      |      |

| Figure 8: GPI-2 latency on the UNIMEM Prototype system (Sockets over UNIMEM)                    |      |

| Figure 9: State-of-the-art MPICH design, showing UNIMEM OFI provider                            |      |

| Figure 10: Future optimized UNIMEM MPI implementation with overriding collectives               |      |

| Figure 11: Roundtrip latency for small message sizes.                                           |      |

| Figure 12: Throughput for large data payloads.                                                  |      |

| Figure 13: DVFS mechanism                                                                       | . 25 |

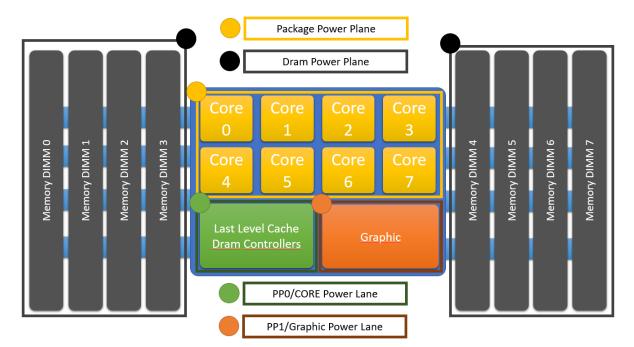

| Figure 14: RAPL power domain                                                                    |      |

| Figure 15: Monitor runtime                                                                      |      |

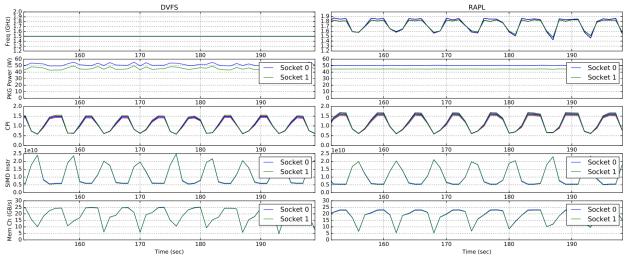

| Figure 16: Comparison of DVFS and RAPL (Time window of 50 seconds)                              |      |

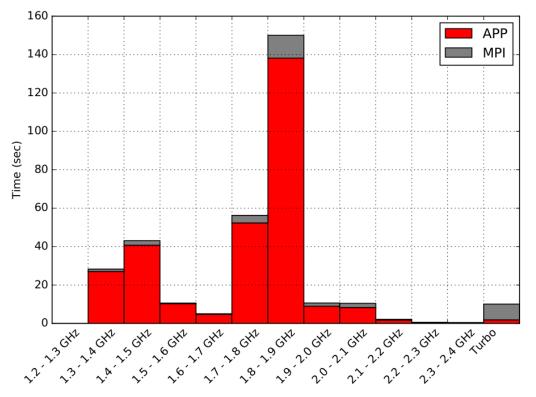

| Figure 17: Sum of MPI and application time grouped by interval frequencies                      |      |

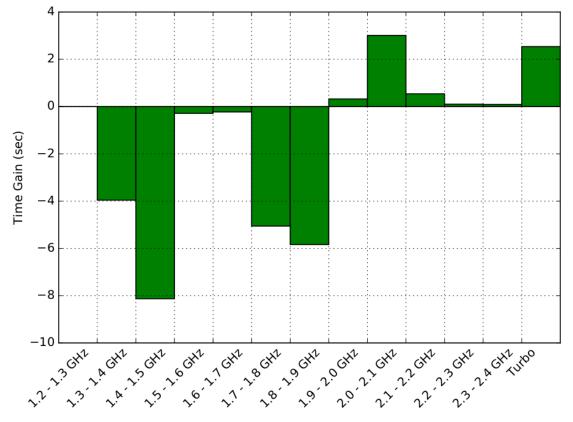

| Figure 18: Time gain of DVFS w.r.t RAPL grouped by interval frequencies                         | . 31 |

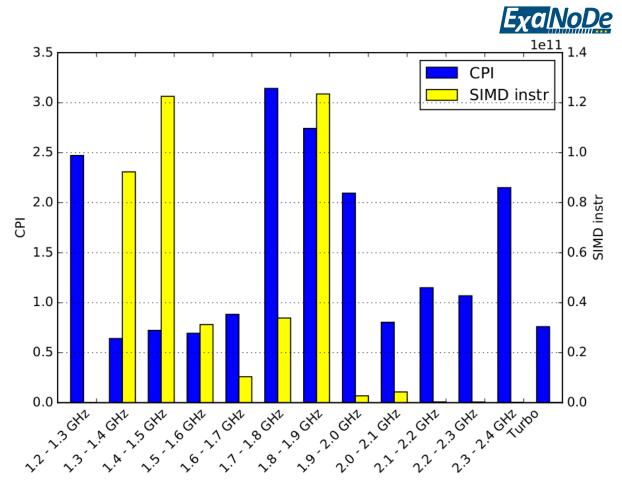

| Figure 19: Average CPI and number of AVX instructions retired on different interval             |      |

| frequencies                                                                                     | . 32 |

# List of abbreviations

| Term             | Definition                                                |

|------------------|-----------------------------------------------------------|

| ACPI             | Advanced Configuration and Power Interface                |

| API              | Application Programmer Interface                          |

| APP              | Application rogrammer interface                           |

| BW (MPI)         | Busy Waiting MPI                                          |

| CPI              | Cycles Per Instruction                                    |

| CPU              | Central Processing Unit                                   |

| DoA              | Description of the Action                                 |

| DSA              | Dynamic Single Assignment                                 |

| DVFS             | Dynamic Voltage and Frequency Scaling                     |

| EAW              | Energy-Aware MPI Wrapper                                  |

| ECED             | Edge and Coherence-Enhancing Anisotropic Diffusion filter |

| FFT              | Fast Fourier Transform                                    |

| FIFO             | First In First Out                                        |

| FPGA             | Field Programmable Gate Array                             |

| FSP              | First Step Problem                                        |

| GAS              | Global Address Space                                      |

| GAS              | Global Address Space Networking                           |

| GASPI            | Global Address Space Programming Interface                |

| GPL              | GNU General Public License                                |

| GPU              | Graphics Processing Unit                                  |

| GSAS             | Global Shared Address Space                               |

| HLS              | High-Level Synthesis                                      |

| IILS<br>IB (MPI) | Interrupt-based MPI                                       |

| ILP              | Integer Linear Programming                                |

| IMC              | integer Einear i fögrämming                               |

| ISP              | <i>i</i> -th Step Problem                                 |

| LLC              | <i>i</i> -th step i roben                                 |

| MCTP             | (Fraunhofer's) Multicore Thread Package                   |

| MPI              | Message Passing Interface                                 |

| MPSD / MPMD      | Multiple Program Single/Multiple Data                     |

| NUMA             | Non-Uniform Memory Access                                 |

| OFI              | OpenFabrics Interface                                     |

| OS               | Operating System                                          |

| OTC              | Optimal Thermal Controller                                |

| PE               | Optimal Thermal Controller                                |

| PGAS             | Partitioned Global Address Space                          |

| PID              | Proportional–Integral–Derivative (controller)             |

| PMPI             | MPI Profiling interface                                   |

| PMU              | with the total interface                                  |

| PoC              | Proof of Concept (prototype)                              |

| QE-CP            | Quantum ESPRESSO Car–Parrinello                           |

| RAPL             | (Intel) Running Average Power Limit                       |

| RDMA             | Remote DMA (Direct Memory Access)                         |

| RTM              | Reverse Time Migration                                    |

| SIMD             | Single Instruction Multiple Data                          |

| SPSD / SPMD      | Single Program Single/Multiple Data                       |

| SMP              | Symmetric Multiprocessor                                  |

| TDP              | Thermal Design Power                                      |

| IDE              | inemia Design rower                                       |

| TMC | Thermal-aware Task Mapper and Controller |

|-----|------------------------------------------|

| UDP | User Datagram Protocol                   |

| VMR | Virtual Memory Region                    |

# 1 Introduction

The ExaNoDe project is developing a unique HPC system architecture based on the UNIMEM architecture, which is also the basis for the related projects EUROSERVER [3], ExaNeSt [4] and EuroEXA [5]. A system that implements UNIMEM consists of a number of computational nodes connected through a custom network. Each node typically contains multiple processing cores, which communicate amongst themselves using coherent shared memory as provided by the hardware. Distinct nodes communicate using UNIMEM's global address space (GAS), which provides non-coherent load–store and RDMA access to any other remote node. The UNIMEM hardware architecture is exposed to user space via the Global Shared Address Space (GSAS), user-space RDMA, mailbox and remote allocator APIs defined in D3.6 [1] (which was due in project month 12).

For easier programming, the application developers will be provided with standard and portable programming interfaces through the runtime systems and communication libraries described in this deliverable. This approach allows applications to take advantage of the characteristics of the ExaNoDe system architecture and UNIMEM architecture, without them having to be ported to a specific API and without the application developer needing to understand in detail the associated performance tradeoffs.

Section 2 describes the work done on integrating the task-based programming models OmpSs and OpenStream with UNIMEM. In addition work done to support FPGA programming has been included in the section as well as the choice of mini-application to test the programming model with.

OmpSs is a task-based programming model that extends OpenMP with new directives for asynchronous parallelism and heterogeneous devices such as GPUs and FPGAs. In ExaNoDe, the cluster implementation of OmpSs runtime system Nanos6 is being leveraged as the basis for efficient runtime support for offloading tasks across nodes on the UNIMEM architecture with the help of the underlying MPI communication API. OmpSs already supports offloading of tasks to FPGAs, using High-Level Synthesis (HLS), and it is being ported to the Xilinx UltraScale+ FPGA in the AXIOM Project [6]

OpenStream is a task-based data-flow programming model also implemented as an extension to OpenMP, and designed for efficient and scalable data-driven execution. OpenStream has explicit dependencies in the source program marked using streams. Compile-time transformations map each task's memory accesses to private input and output buffers. The OpenStream runtime system controls memory allocation, task placement and RDMA memory transfers between tasks. OpenStream is supporting OpenCL to exploit FPGAs and is integrating the EcoSCALE [7] High-Level Synthesis (HLS) toolchain.

Section 3 describes the integration of the communication APIs GPI and MPI in the ExaNoDe prototype. In addition work done to support FPGA programming has been included in the section as well as the choice of mini-application to test the programming model with.

GPI is an open-source communication library that implements the GASPI standard PGAS API. It provides a portable and lightweight API that leverages remote completion and one-sided RDMA-driven communication, both being efficiently supported by the UNIMEM architecture. UNIMEM dependent module of GPI have been identified, integrated with UNIMEM and integrated with an emulation framework to socket layer of UNIMEM, the software has been tested on the remote prototype. A setup of a small test system consisting of Xilinx Ultrascale+ FPGAs and ARM 64-bit in one package is foreseen to build up the necessary FPGA support.

MPI is the standard message-passing API supported by all serious HPC systems and employed by the vast majority of scientific applications. Efficient support for MPI is mandatory for any HPC system or prototype, and MPI support is an important output from ExaNoDe WP3 that is needed by the ExaNeSt project and will be further optimized in the EuroEXA project. The OmpSs integration of UNIMEM will be based on MPI. The coupling will be done with the lowlevel network interface OFI on which the MPI implementation MPICH is built.

Section 4 describes thermal and power management. These technologies will be made available and potentially integrated into the optimized implementations of GPI, OmpSs, OpenStream and MPI.

The runtime systems and communication libraries are being prototyped and developed using (a) remote access to the multi-board prototype hosted at FORTH in Crete, which provides functional verification on real hardware, and (b) software emulation of the UNIMEM APIs using a software layer provided by FORTH and UOM. The latter provides the ability to perform substantial development work on a local machine.

The runtime systems and communication library will be tested and evaluated using the miniapplications from WP2 (from D2.1 [8]) as indicated in Table 1.

|                                                                                        | MPI                  | GPI-2                                         | <b>OmpSs</b> (clusters)                                             | OpenStream                                                     |  |

|----------------------------------------------------------------------------------------|----------------------|-----------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------|--|

| Programming<br>model                                                                   | Message PGAS passing |                                               | Tasks with argument<br>directionality<br>(input/output)             | Tasks with explicit<br>dependencies specified<br>using streams |  |

| Data visibility                                                                        | Local to MPI process | Global                                        | Global                                                              | Global                                                         |  |

| Mapping work to nodes                                                                  | Manual               | Manual                                        | Runtime system                                                      | Runtime system                                                 |  |

| Language type                                                                          | API API              |                                               | Language extension (Pragmas)                                        | Language extension<br>(Pragmas)<br>SPSD / SPMD                 |  |

| Execution style MPMD                                                                   |                      | MPMD                                          | SPSD / SPMD                                                         |                                                                |  |

| Inter-nodeExplicitExplicitcommunication(message<br>passing)(one-sided<br>asynchronous) |                      | (one-sided                                    | Implicit<br>(runtime system based<br>on argument<br>directionality) | Implicit<br>(runtime system based or<br>streams)               |  |

| Work scheduling                                                                        | Manual               | Manual                                        | Runtime system                                                      | Runtime system                                                 |  |

| Base language(s)                                                                       | C, C++,<br>FORTRAN   | C, FORTRAN                                    | C, FORTRAN, CUDA                                                    | С                                                              |  |

| WP2 Mini-app                                                                           | All                  | GPI test suite,<br>separate stencil<br>kernel | MiniFE                                                              | HydroC, MiniFE and<br>NEST                                     |  |

#### Table 1: Comparison of runtime systems and communication libraries

# 2 Runtime systems

The work on two task-based runtime systems, OmpSs and OpenStream, is presented in this section. Both OmpSs and OpenStream extend the programming language (C, FORTRAN or CUDA in case of OmpSs, C in case of OpenStream) with pragmas. The internode communication is implicit. OmpSs and OpenStream will exploit UNIMEM in their cluster implementation.

# 2.1 OmpSs

This section was contributed by BSC.

This section presents the contributions of BSC related to the OmpSs programming model and the Nanos runtime system for distributed execution. In Section 2.1.1 we discuss the latest features of OmpSs which enable more opportunities for exploiting parallelism at the programming model level. Section 2.1.2 presents the distributed memory version of Nanos6, the new implementation of the OmpSs programming model. Section 2.1.2.1 presents the memory model of the distributed memory Nanos6, Section 2.1.2.2 describes the execution model, showing how tasks can be offloaded to nodes of the cluster transparently to the programmer, Section 2.1.2.3 discusses the design of the communications layer of the runtime system and finally, in Section 2.1.2.4 we show some initial results from popular linear algebra kernels ported to the OmpSs programming model.

## 2.1.1 Introduction to OmpSs-v2

OmpSs [9] is a task-based parallel programming model aimed to provide scalability and malleability without significant programming effort. OmpSs-v2 [10] is an extension of the programming model, initiated in the INTERTWinE [11] Project that increases the scalability of applications by integrating more efficiently nested tasks, a natural way to decompose a bigger problem in finer-grain computational tasks, with task dependencies.

## 2.1.1.1 Fine-grained release of dependencies across nesting levels

Task-based programming models that support dependencies and nesting normally require a the invocation of a synchronisation primitive at the end of the task, e.g. an OpenMP *taskwait*

```

#pragma omp task depend(inout:a,b) weakwait

//Task T1

{

a++; b++;

#pragma omp task depend(inout: a)

//Task T1.1

a += ...;

#pragma omp task depend(inout: b)

//Task T1.2

b += ...;

}

#pragma omp task depend(in: a)

//Task T2

.... = .... + a + ....;

#pragma omp task depend(in: b)

//Task T3

.... = .... + b + ...;

```

#### Figure 1: Fine-grained release of dependencies using the weakwait construct of OmpSs-v2

pragma, which blocks the task until all its subtasks have finished. This is required in order to preserve the correct semantics of dependencies across tasks. Prior work in the INTERTWinE Project introduced the OmpSs-v2 *weakwait* clause to *task* pragma. The *weakwait* clause

implicitly inserts a taskwait after the execution of the task, which allows the runtime system to understand that no more subtasks are going to be created and the dependencies of the task that do not need to be enforced any more can be released incrementally.

For example in Figure 1 we have a code snippet with task T1 that depends on variables a and b and has two subtasks T1.1 which depends on a and T1.2 which depends on b, task T2 which depends on a and task T3 which depends on T3. Without the weakwait construct T1 would need to include a *#pragma omp taskwait* at the end of the task body. T2 and T3 would wait until the completion of T1 which would happen only after T1.1 and T1.2 have finished. With the weakwait clause once the body of T1 exits only the live dependencies of T1 need be enforced, i.e., if T1.1 has not yet finished the dependency from T1 to T2 becomes a dependency from T1.1 to T2, so that T2 can start even if T1.2 has not finished yet. This allows the discovery of more parallelism dynamically.

In the previous example, in order to release dependencies this way task T1 needs to finish execution. However, it might be useful to release dependencies while the body of the parent task is still executing, e.g., the task knows that it will use some data only at the beginning. In order to enable this functionality OmpSs-v2 introduces a new directive:

#### #pragma omp release depend(...)

which releases all the dependencies in the list of the depend clause.

#### 2.1.1.2 Weak dependencies

Section 2.1.1.1 presents how OmpSs-v2 allows the early release of dependencies from inner to outer nesting-levels in a fine-grained fashion. However, where nesting is used, it is likely that the outer nesting levels define dependencies in a coarser granularity. Even if some elements of the depend clause of the outer task is only needed by its subtasks, its execution and eventually the creation of the subtasks will be deferred and discovery of parallelism, suspended.

OmpSs-v2 extends the depend clause with the *weakin, weakout* and *weakinout* dependency types. Semantically, these types define dependencies equivalent to the non-weak types. When a task declares weak dependencies, though, it signifies that it will not access itself the data, only its subtasks will do, hence the task is allowed to start its execution, which will allow it to create the subtasks.

As a result, early release of dependencies and weak dependencies, together in action can potentially result in increased parallelism discovery while expressing the applications using nesting which is very natural for a large number of problems.

#### 2.1.2 Nanos6 runtime system on distributed memory

OmpSs-v2 is implemented in Nanos6 the successor of the Nanos++ runtime system. The choice to implement a new runtime system, rather than implementing OmpSs-v2 as extensions in Nanos++, is guided from the requirements of backwards compatibility for OmpSs applications as well as better maintainability of the Nanos6 codebase in comparison with Nanos++.

Nanos6 provides a new version for the distributed memory runtime implementation in the ExaNoDe project, which incorporates the features of the OmpSs-v2 programming model and introduces a novel memory model, task offloading mechanism and communication layer.

#### 2.1.2.1 Nanos6 memory model

The distributed memory version of OmpSs developed in the ExaNoDe Project provides a Partitioned Global Address Space (PGAS) model abstraction layer for the memory view of the

system. This OmpSs memory layout is general-purpose and applicable to an implementation for any cluster, but it enables future work, in ExaNoDe or EuroEXA, to take advantage of the UNIMEM shared memory architecture. The OmpSs memory model presents the distributed physical address space of the nodes involved in the computation as a single address space which is accessible by every compute node of the cluster. As a result, on conventional clusters that require physical memory copies among nodes of the cluster, the programmer does not need to explicitly program these data transfers, as they are handled by the Nanos6 distributed memory runtime using MPI. The current implementation will target UNIMEM via the UNIMEMoptimized MPI library. We will consider the potential benefit of future optimizations to use the native UNIMEM API to eliminate the data transfers on UNIMEM platforms, while maintaining software compatibility with traditional distributed memory clusters.

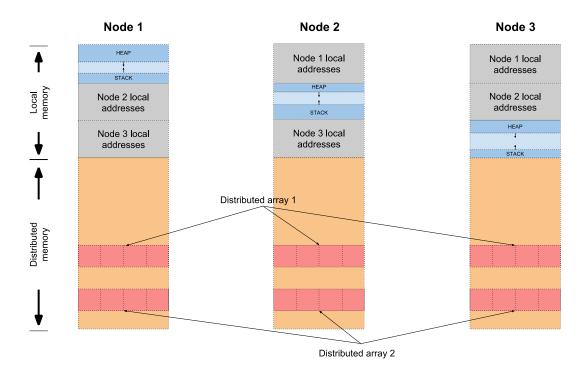

Figure 2 shows the layout of the virtual memory of the cluster nodes managed by the Nanos6 runtime system. During initialization Nanos6 maps in every node a virtual memory region (VMR) large enough to handle the maximum memory requirements of the OmpSs application. The starting address of these VM regions is the same on every node. This is necessary in order to facilitate the transfer of data across nodes without having to apply address translation across nodes. Memory requests are served through custom allocators of the Nanos6 runtime system. Subsequently, Nanos6 divides each VMR into two distinct regions, which have different allocation semantics.

The lower addresses of the VMR are reserved for conventional local memory allocations, i.e., stack and normal heap allocations. Nanos6 divides this set of addresses equally among the nodes of the cluster. This means that every address within this region is used to store the local data of one particular node of the cluster. The rest of the nodes of the cluster use these addresses whenever they need to bring local data of the said node, temporarily. This simplifies the process of moving data around the cluster, since it eliminates the need for address translation.

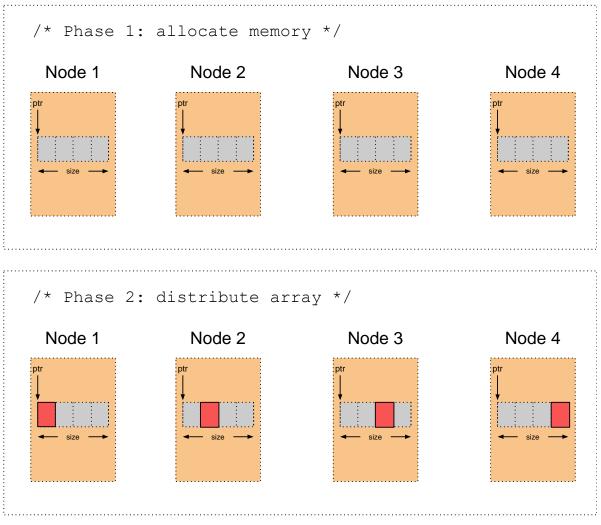

The higher addresses of the VMR are reserved for *distributed allocations*. An allocation from this memory region is implemented inside the runtime system as a collective operation across all nodes of the cluster. Figure 3 describes the operation of a distributed allocation. Firstly, the

whole distributed array is allocated in every cluster node at exactly the same memory range [ptr, ptr + size). Subsequently, each node becomes the *home node* of one part of the array. This means that by default, the latest produced data of a subrange of the array will be stored in its home node. If during execution, a range  $[subrange_ptr, subrange_ptr + size)$  needs to be used by a task that is scheduled on a node different than its home node, a memory transfer will be initiated from the home node of the subrange. When a node fetches a range of data from its home node it uses the same range of addresses as its home node does. Those virtual addresses are available also locally, since during the allocation of the array these addresses were allocated on every node of the cluster. In this way, Nanos6 does not have to do address translation when it moves distributed data across the cluster nodes. The way an array is distributed to home nodes is controlled by the programmer who can choose the distribution policy. Information about the distribution policy of arrays can be used later by the Nanos6 scheduler in order to make decisions based on locality criteria. Thus the distribution policy is meant to be chosen according to the access patterns of the application.

Figure 3: Distributed allocation in Nanos6 is a collective operation. The array is allocated first on all nodes and then logically distributed across them

#### 2.1.2.2 Nanos6 execution model

The memory model is coupled with the task-parallel semantics of OmpSs for defining computations. The programmer defines tasks i.e., computational units that operate on ranges of data located on the address space.

Nanos6 uses a master-slave architecture. The OmpSs application begins executing on the *master* node, similarly to the shared-memory flavour of the runtime. The code is executed serially and whenever a #pragma omp task directive is encountered a new task is created and becomes available for concurrent execution once its dependencies are resolved. When running on distributed memory, the scheduler of Nanos6 can also decide to offload tasks to *slave*, or else *remote*, nodes once they are ready for execution, i.e., all their strong dependencies have been resolved.

During execution, the scheduler takes decisions regarding the node onto which the task should be offloaded. Before a remotely-executed task executes its body function, the runtime system copies any non–node-local data to the node that the task will execute on. The programmer needs to declare all the dynamically allocated data that the task uses and the way the task will handle them using the dependencies clauses: *in(), out(), inout(), weakin(), weakout()* and *weakinout()*. When executing on distributed memory, in addition to declaring the dependencies among tasks, these clauses provide the necessary information about data transfers that must be performed by the runtime before executing a task.

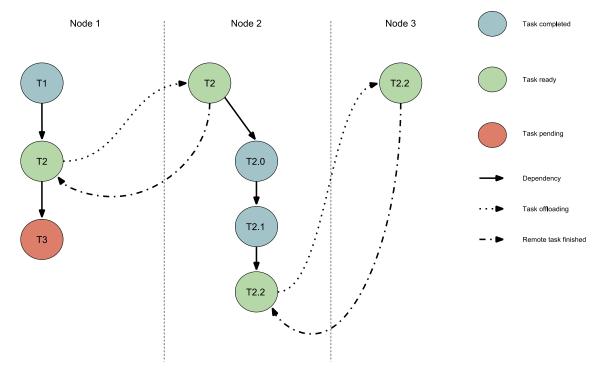

Figure 4: Nanos6 task offloading. A ready task can be offloaded to a remote node. All tasks with a dependency on the offloaded task will wait until the offloaded signals its completion.

Figure 4 presents an example of the execution model of Nanos6 for distributed memory systems. In this example, when task T2 becomes ready for execution, the scheduler decides to offload it to Node 2. The original task is marked as an *offloaded* task and it remains in the memory of Node 1 so that the dependencies within Node 1 are preserved. Task T3 on Node 1 has a dependency on T2 and as a result it will not be ready until the T2 is marked as complete. This will happen once the *remote* T2 sends a message to the offloaded T2 signaling its completion. Along with the task T2, Node 1 sends to Node 2 information regarding the location of all the data that T2 takes as input (*in()* and *inout()* dependencies). Once the access information for all the input arguments of the remote task T2 on Node 2 is received the task T3 is ready for execution. In addition, the remote T2 creates three subtasks. The first two are executed locally, but T2.2 is offloaded by the scheduler from Node 2 to Node 3. The parent task T2 will not be marked as complete until the remote T2.2 finishes. When T2.2 on Node 3 finishes it sends a message to Node 2 along with access information about all the output dependencies i.e., *out()*

and *inout()*. This information is then propagated from Node 2 to Node 1. At this point T3 can start execution, knowing the location of all the output accesses of T2. This example shows how Nanos6 uses the dependency system to propagate information regarding the location of all the data of the OmpSs application. This scheme allows us to handle all the data transfers without the need of a software directory, which simplifies the design and implementation and minimizes the amount of communication among the cluster nodes.

#### 2.1.2.3 Communication Layer

The implementation of Nanos6 requires communication among the cluster nodes for exchanging *command* and *data transfer* messages. Command messages include all the messages for offloading tasks, synchronization of nodes, sending information regarding the location of data and initiating data transfers. Data transfer messages are used to transfer data regions among nodes.

The communication layer of Nanos6 operates as an abstraction layer that decouples the rest of the components of the runtime system from the actual library that is used to implement the actual network transfers. This design is very modular since it allows the network communication layer to be transparently implemented on top of different libraries and allows the user to choose the most desirable implementation at runtime.

For ExaNoDe we have implemented the communication layer of Nanos6 on top of standard MPI. This provides compatibility with all HPC systems that implement the MPI standard, making it a very appealing choice. In particular, the port of MPI to the UNIMEM architecture will allow Nanos6 to run on any UNIMEM platform without modifications. In future work, in ExaNoDe or EuroEXA we will consider the benefit of eliminating the data transfer messages using the native UNIMEM API, while maintaining software compatibility with traditional distributed memory clusters.

#### 2.1.2.4 Preliminary results

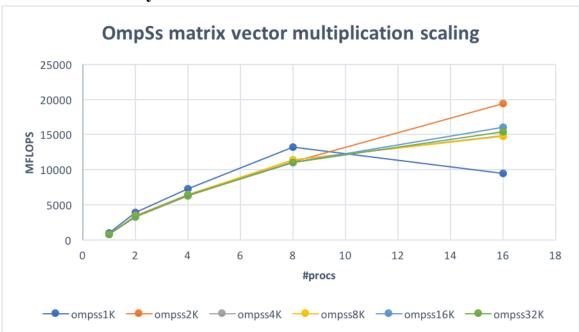

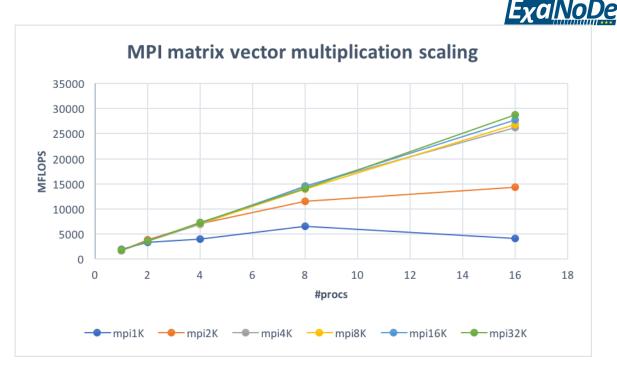

Figure 5: Scaling of a matrix vector multiplication operation implemented in OmpSs with Nanos6 Clusters.

Figure 6: Scaling of a matrix vector multiplication operation implemented in MPI

We have performed an evaluation of the initial implementation of Nanos6 using various BLAS kernels ported to OmpSs-v2, and compared them with the equivalent MPI implementations. Figure 5 and Figure 6, respectively, show the scaling of a matrix–vector multiplication operation in OmpSs and MPI measured on the MareNostrum 4 supercomputer. The results show that, compared with MPI, Nanos6 currently faces scalability issues when the problem sizes increase. This could be attributed to various issues, e.g. the scheduler implementation of Nanos6 or overheads related to the offloading of tasks to nodes and caching data to remote nodes. We are currently investigating these bottlenecks with the assistance of Extrae and Paraver, which are the tracing and performance analysis tools that have been developed from BSC and are being integrated in Nanos6.

# 2.2 OpenStream

This section was contributed by UOM.

#### 2.2.1 Introduction to OpenStream

OpenStream [12] is a task-parallel, data-flow programming model implemented as an extension to OpenMP. It is designed for efficient and scalable data-driven execution; shared-memory programming is allowed for fast prototyping, essentially following the OpenMP syntax, but additional information must be provided by the programmer, using a dedicated syntax, in order to take advantage of OpenStream optimizations. In particular, OpenStream enables programmers to express arbitrary dependence patterns, which are used by the runtime system to exploit task, pipeline and data parallelism. Each data-flow dependence is semantically equivalent to a communication and synchronization event within an unbounded FIFO queue. Pragmatically, in the original shared-memory instantiation, this is implemented by compiling dependences as accesses to task buffers dynamically allocated at execution time: writes to streams result in writes to the buffers of the tasks consuming the data, while read accesses to streams by consumer tasks are translated to reads from their own, task-private buffers.

Compared to the more restrictive data-parallel and fork-join concurrency models, task-parallel models enable improved scalability through load balancing, memory latency hiding, mitigation of the pressure on memory bandwidth, and as a side effect, reduced power consumption.

Currently developed at UOM, OpenStream further takes advantage of the information provided by programmers on task dependences to aggressively optimize memory locality through dynamic task and data placement.

#### 2.2.2 Exploiting UNIMEM in OpenStream

OpenStream relies on a private-by-default strategy for handling communication between tasks, which means that despite a shared-memory view from the programmer's perspective, communication is more akin to message-passing than to concurrent shared-memory communication. This is made possible by requiring programmers to provide additional information on how data is accessed within tasks. This information is used at compile time to generate the appropriate modifications to memory accesses to achieve Dynamic Single Assignment (DSA). OpenStream tasks compute on data available in input buffers and write data in output buffers, each belonging to a unique task reading from them. This data-flow execution model is a perfect match for the UNIMEM memory model, providing a straightforward mapping of communication on top of RDMA and minimizing the reliance on global atomics. Furthermore, the privatization of data communicated between tasks is the key to enable the runtime to fully control the locality of memory allocation and of task placement. OpenStream relies on the inter-node atomics provided in the UNIMEM memory model to implement low-level runtime algorithms, such as dynamic load balancing, inter-node synchronization and locality-aware scheduling and memory allocation. This is further discussed in Section 4.2.

Further optimization of the behavior of the OpenStream runtime will be possible if UNIMEM permits RDMA and atomics to be used within the same memory regions. This has been one of the key challenges to port OpenStream as it has required splitting the data-structures used for managing memory and task placement across separate memory regions while ensuring that data and meta-data remain coherent.

The development of concurrent data-structures and algorithms on memory models that do not provide sequential consistency is patently error-prone and time consumming. Testing poses significant challenges as errors may only manifest when specific interleavings of memory operations occur – behavior which can be impossible to exhibit on emulation or on prototypes where the timing is substantially different than the target hardware. This problem is further compounded when the memory model is not uniform across all execution units as node-local behavior will differ from inter-node behavior. We expect that a substantial number of issues are likely to become apparent when executing on increasingly advanced hardware that allows more memory interleavings to occur.

For example, we expect that the behavior of atomic operations provided in UNIMEM will have an impact on our work-stealing load-balancing algorithm if there is an asymmetry between the success rates of local and remote atomic operations. Such an asymmetry would introduce a bias in the way our algorithm works, which in turn would translate into poor work distribution across the machine. As we further discuss below, this is critical for OpenStream programs as we do not assume an initial distribution of data and work across the machine.

#### 2.2.3 Implementation

**Communication** is automatically managed by the OpenStream runtime system. Part of the work is done at compilation time, by privatizing all data dependences between tasks and introducing runtime hooks for setting up remote memory operations. This step enables the runtime to determine which data is locally available and which data needs transferring, then initiate the memory transfers and determine when all data required for execution is finally

available. As no worker is waiting for data to be transferred, a good load balance will ensure that computation and communication is fully overlapped.

**Memory and work placement** are driven by two main algorithms [13] [14]. The main mechanism for nodes and workers to acquire work is randomized work-stealing. This allows to balance the workload across compute resources, but may be inefficient with respect to the amount of communication it generates as tasks are randomly acquired by workers across the entire machine. Dependence-aware memory allocation and work-pushing allow to reduce the amount of communication required by moving tasks to nodes that will require the least data movement.

**Multiple node startup** is managed directly within the OpenStream loader rather than relying on an external tool, and uses the *remoteFork* facility. The startup procedure instantiates a core process on each node and initialises the OpenStream communication and scheduling data structures, then allows the local processes to set up a team of worker threads on each node. There is no initial distribution of work as OpenStream relies primarily on hierarchical workstealing for load-balancing. As soon as a node is ready to start executing tasks, it starts attempting to steal work from neighboring nodes.

In later stages of execution, once data is distributed across the machine, locality-aware workpushing will complement work-stealing by sending tasks that require remote data to be executed on the node where most of their inputs are located. While this approach helps reduce the amount of data movement overall, it may lead to poor load-balance if it is used on its own as it will have a tendency to concentrate data and work on a subset of nodes. Randomized work-stealing is therefore still required to ensure that computation is reliably distributed across all nodes, further enabling the possibility of seamlessly bringing new nodes online during execution.

#### 2.2.4 ExaNode Mini-app

Due to the availability of the HydroC mini-app in multiple parallel programming models, including a C+OpenMP version, this has been the primary target for porting to OpenStream. The initial translation from OpenMP parallel loops to OpenStream tasks relying on shared memory communication was straightforward and yields identical performance results on uniform shared memory multi-core platforms. This compatibility behavior is allowed in OpenStream to facilitate porting efforts, however, this version cannot be compiled directly to execute on multiple UNIMEM nodes.

In a second step, the OpenStream implementation was converted from shared-memory dataparallel execution to pure data-flow, where tasks communicate exclusively through privatized streams. This step was complicated by the frequent use of shared memory pointer arithmetic when communicating partial results between different computation phases of HydroC, but it is essential to enable multi-node execution and to allow showcasing the advantages of UNIMEM RDMA communication overlapping computation.

The porting effort has now shifted towards optimizing the data-flow implementation, in particular focusing on eliminating over-synchronization between computation steps, and towards integration in the UNIMEM emulation framework and the physical prototypes.

#### 2.2.5 Towards FPGA integration

To exploit the Field-Progammable Gate-Arrays (FPGAs) that represent the bulk of the computational power in the ExaNoDe system, we have made the decision to extend OpenStream with OpenCL support, enabling programmers to specify multiple versions for the work function of each task, written either in C (possibly wrapping code in other sequential

languages) or in OpenCL. These versions are managed by the OpenStream dynamic scheduler, which decides at runtime on the best target for each kernel.

Currently, OpenStream is able to schedule the different kernel versions across CPU cores and multiple, heterogeneous OpenCL devices (e.g., CPU cores + AMD APU + discrete GPU) and we are currently optimizing the scheduler heuristics for dynamically adapting the target device based on the observed cost of communication and compute time on each available resource for the different types of tasks.

This preliminary work has cleared a path to the next step, which is to integrate the OpenStream environment with the EcoSCALE high-level synthesis toolchain to take advantage of the Xilinx Ultrascale+ FPGAs that will be available on the ExaNoDe system. The design of the current implementation was chosen to maximise the flexibility of the OpenStream framework and we expect to be able to integrate FPGAs in the OpenStream resource model and scheduler.

## 2.3 Parallel runtime support

This section was contributed by UOM.

#### 2.3.1 Introduction

In order to maximize the efficiency of execution, both in terms of performance and energy, and to exploit fully the massive parallelism provided by the ExaNoDe architecture, it is essential to optimize performance-critical aspects of the runtime. In particular, UOM is focusing on dynamic load balancing through work-stealing, dynamic scheduling for memory locality and synchronization.

#### 2.3.2 Optimized runtime support

UOM has ported the current state-of-the-art implementation [14] of work-stealing dynamic load-balancing based on Chase and Lev's algorithm for intra-node load balancing, as well as the fastest hybrid barrier synchronization implementation [15] for a single node. This first step is essential even with the new UNIMEM memory model because these algorithms are very sensitive to latency and therefore cannot rely on a uniform view of the memory.

In a second step, UOM has implemented a functional unoptimized work-stealing library on top of UNIMEM for inter-node load balancing, which is integrated with the intra-node algorithm in the form of hierarchical work-stealing, whereby work is sought in widening neighbourhoods. This implementation relies on the remote atomic operations provided by UNIMEM, and for which UOM has developed an emulation layer that integrates with FORTH's RDMA emulation library. Furthermore, to minimize the overheads incurred by memory transfers between nodes, UOM has developed locality-aware allocation and scheduling optimizations that deliver above 94% locality and up to 99% locality and  $5\times$  speedup over hierarchical work-stealing on 24 nodes [14]. While this study was conducted on a classical NUMA machine, the results are likely to translate into similar locality benefits, albeit with new tradeoffs that will require further investigation, on an ExaNoDe platform once ported.

# **3** Communication Libraries

Two communication libraries, the message passing MPI and the partitioned global address space library GPI, will use UNIMEM. Compared to the runtime systems the inter-node communication with the UNIMEM communication will be explicit. Thus a direct coupling between MPI/GPI components and UNIMEM becomes center-stage in this section. For GPI the focus is on one-sided asynchronous messages, whereas the MPI work will be foucessed on message passing.

# 3.1 GPI

This section was contributed by FHG.

#### 3.1.1 Introduction to GPI

The Fraunhofer GPI (Global Address Space Programming Interface) open-source communication library is an implementation of the GASPI standard [16], freely available to application developers and researchers. GASPI stands for Global Address Space Programming Interface, and it is a Partitioned Global Address Space (PGAS) API that aims to provide extreme scalability, high flexibility and failure tolerance for parallel computing environments.

GASPI aims to initiate a paradigm shift from bulk-synchronous two-sided communication patterns towards an asynchronous communication and execution model. It leverages remote completion and one-sided RDMA-driven communication in a Partitioned Global Address Space. The asynchronous communication enables a perfect overlap between computation and communication. The main design idea of GASPI is to have a lightweight API ensuring high performance, flexibility and failure tolerance. More details about GPI can be found in deliverable D3.1 or on the GPI web page (http://www.gpi-site.com/gpi2/).

## 3.1.2 Exploiting UNIMEM in GPI

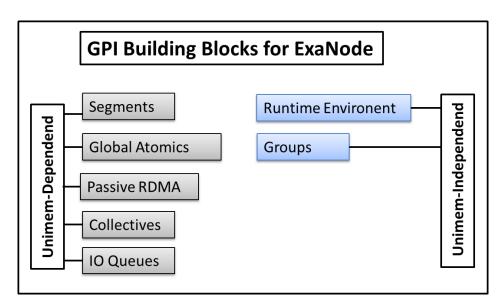

Figure 7: PI Building blocks for ExaNoDe architecture support

The UNIMEM independent modules (Runtime Environment and GPI Groups) can be developed/ported without any knowledge of the final hardware characteristics and interface descriptions of the ExaNode/UNIMEM architecture. Both modules are able to run over a secondary network using TCP/IP for data exchange. This makes it possible to start early implementations of these components within the ExaNoDe project. The communication

interface for these modules will be RDMA over Sockets, one of the transport layers of UNIMEM.

Both independent modules have now been ported to the aarch64 architecture and can used on top of socket-interfaces of UNIMEM.

All UNIMEM-dependent modules, such as pinned memory segments, global atomics (and related memory areas), passive RDMA, collectives and one-sided reads and writes managed by IO-queues are hard to implement without detailed knowledge of the behaviour of the interconnect interface. Therefore an emulation library has been developed that implements most of the current functionality as described in [17]. This emulation library allows early tests on a standard x86\_64 SMP system without the need to have real prototype hardware available on site. The remote system provided has proven not to be stable enough to run integration tests. All dependent modules have been implemented on top of the emulation framework and early tests were successful.

Some design decisions made by Forth for the user level RDMA Interface of UNIMEM will not allow GPI Applications to run directly on this layer without re-compilation and re-coding. In addition to that, the prototype systems and the available UNIMEM libraries are not yet stable enough for developments like GPI or practical tests and benchmarks. To ensure that a working GPI version for the ExaNoDe architecture is ready at the end of the project, we have ported the dependent GPI Modules from our emulation framework to the socket layer of UNIMEM. At the current stage of the project it is crucial to be able to start gpi\_run. Here further work on UNIMEM needs to be done (as pointed out in Section 3.1.5.

This workaround allows us to further improve the individual GPI-Submodules and to continue the developing process without time-consuming delays (Erreur! Source du renvoi introuvable.). A running GPI communication library is the basis for the development of one-sided micro benchmarks and mini-applications on top of the ExaNoDe hardware.

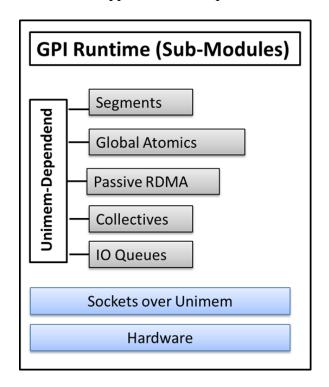

Figure 8: GPI BuildingBlocks of UNIMEM

#### 3.1.3 Design of preliminary software implementation

The following sub-chapters are describing the implementation of dependent GPI Modules (Erreur ! Source du renvoi introuvable.) on top of UNIMEMs socket layer.

#### 3.1.3.1 GPI Segments

GPI Segments can be created and deleted by using standard system routines like e.g. malloc and free. There are no size or alignment constraints on these segments as we have today with RDMA memory segments on most other interconnects. The allocation time will also be fast as we can use copy on write (cow) mechanisms compared to pre-pinned continuous memory segment allocations.

#### 3.1.3.2 GPI IO-Queues

GPI applications trigger one-sided RDMA reads and writes by placing communication tokens into GPI IO-Queues. The status of a single token or a group of tokens can be determined at any time by calling a wait operation on a given queue. The wait operation returns a status array filled with the status of all completed read and write operations at that time. To enable nonblocking functionality for all worker threads within posting and wait calls, a background communication thread will be spawned internally. This special thread takes care of all the ongoing communications on all GPI queues and fills up the status arrays. As the communication takes place on top of sockets, the thread does not have to poll for io-operations or completions. The operating system can schedule this thread when data can be sent or peer data have received for one of the active queues.

## 3.1.3.3 GPI Collectives

In a first design GPI Collectives can be implemented by using internal GPI Segments and IO-Queues as described in Sections3.1.3.1 and **Erreur ! Source du renvoi introuvable.**3.1.3.2.

#### **3.1.3.4 GPI Global Atomics**

GPI currently defines two operations for Global Atomics: Atomic increment and atomic compare and swap (cas). With these two atomic operations in place, global spinlocks can be implemented which can be used to protect global data-structures and variables. As the current semantic for GPI Global Atomics require the immediate return of the previous values, standard IO-Queues cannot be used due to the separation of posting and wait calls. Instead a special IO-Queue will be implemented internally for atomics that combines and interlocks the posting and wait calls.

#### 3.1.3.5 GPI Passive RDMA

Passive RDMA operations cannot be fully offloaded. They need some support from the Operating System so that passive waiting (sleeping) processes/threads can be informed when matching communication data is available. To implement this kind of data transport a special passive IO-Queue as described in 3.1.3.2 will be implemented. For this special IO-Queue the background thread will not fill up any completion arrays. Instead it will trigger one of the system calls like select, poll or epoll to inform waiting worker threads (waiting in GPI\_PASSIVE\_RECEIVE) about available data. The location, status and size of the data is returned to the caller directly from GPI\_PASSIVE\_RECEIVE.

#### **3.1.3.6 Parallel Process Startup**

A parallel startup mechanism like mpi\_run or gpi\_run is still not available yet and standard tools and scripts (e.g. process startup via ssh) cannot be used on UNIMEM. UNIMEM-Processes need to have some kind of parent->child relationship to inherit access rights to memory segments. In addition, environment settings/variables and command line arguments must be communicated to the remote node and setup correctly before a process inside a parallel topology can start. Here we are still in the process of defining an interface that fulfills the requirements for GPI and MPI to start up remote processes.

#### 3.1.4 Suitable ExaNode Mini-app

Beside the GPI test suite a stencil kernel application (such as an BQCD simplified kernel) will be implemented to demonstrate the strength of overlapped and offloaded data communication on ExaNoDe/UNIMEM.

#### 3.1.5 Current Status and Limitations

Current Unimem Limitations for single-sided Communication (GPI-2) are:

- Single memory segment: all GPI- based applications are using at least two or more memory segments during runtime to switch between communication buffers and computation segments (double buffering approach for asynchronous programs). This limitation has been present in the emulation library but is resolved in the UNIMEM software and still needs to be tested.

- Size limitation of the memory segment: 256mb. This size is much too small for real world applications, which typically use up to 16GB to 32GB per node, doing overlapped computations and communications.

- Single communication channel: at least two communication channels are needed to implement overlapped communication: One to post current IO-operations on and another one to poll for previous posted IO-operations as described above.

- Size limitation per IO-operation: 8mb-1byte: for large communication sizes this will produce a lot of overhead (several IO-operations). Stencil code algorithms might be able to run on such a system without any changes, however especially modern machine learning applications might need to use 32-64MB.

- Single RDMA status request: it would be much more efficient to request the status of an array of communication-identifier at once. Single RDMA status requests produce a lot of context switches and other overhead.

- The RDMA functionality should be implemented mostly in userspace and not in kernelspace.

- Atomic operations in UNIMEM cannot use the same memory segments as RDMA IOoperations. Since most of the GPI based applications run atomics and RDMA operations out of the same memory segment, this limitation does not allow pre-compiled GPI-2 binaries to run on top of UNIMEM.

- Atomic operations on UNIMEM need some kind of relationship between affected processes. Access-tokens are distributed over a special startup mechanism which is not compatible with mpi\_run or gpi\_run. Here a startup procedure similar to mpi\_run or gpi\_run is needed to establish a working environment like on any other computing system today.

- The remote UNIMEM prototype systems are not yet stable enough to do intensive tests. To get significant performance data for evaluation, a stable UNIMEM environment is needed.

The above mentioned limitations will be discussed with the FORTH group.

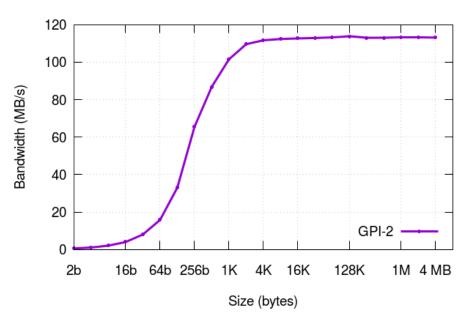

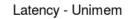

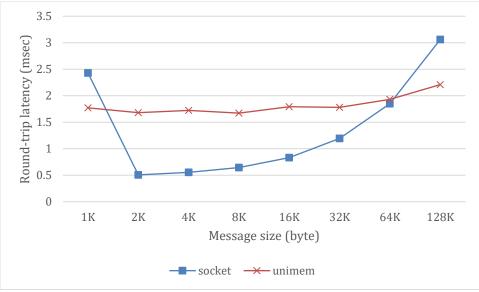

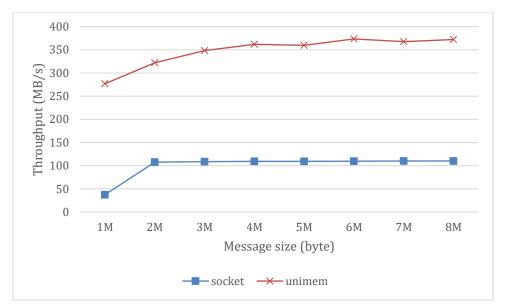

Figure 9 and Figure 10 show first measurements on the remote UNIMEM prototype, namely the GPI-2 bandwidth and latency. The data have been taken on the TRENZ board with the UNIMEM software stack (kernel driver and user-level library). For the latency and bandwidth measurement for each measured point the average of 1000 samples has been taken. For latency a classical ping-pong mechanism was employed, completion time is the time that the pong has been received. For the bandwidth measurement the completion has been signalled by a signal received by UNIMEM. The data values are consistent with the values reported in the MPI implementation in Section 3.2.3. However our measurements start with smaller message sizes. The latency and bandwidth can be compared with measurements taken with Infiniband FDR a few years back both for GPI-2 (and MVAPICH2-1.9). The plots can be found at the GPI web page<sup>1</sup>. The bandwidth for Infiniband FDR saturates at messages sizes about 4kbytes at a bandwidth of 6000 MB/s. The bandwidth is about a factor 50 higher than measured on the Trenz board. The latency of small messages with Infiniband FDR is about 1microsec for 2bytes up to about 2microsec for 2kbytes. This is about a factor of 250 faster than the latency measured with GPI over UNIMEM on the Trenz board. Further optimized capabilities with the GPI implementation are going to be implemented during the coming months.

Bandwidth - Unimem

Figure 9: GPI-2 bandwidth on UNIMEM Prototype system (Sockets over Unimem)

<sup>&</sup>lt;sup>1</sup> GPI web page: http://www.gpi-site.com/gpi2/benchmarks/

Figure 10: GPI-2 latency on the UNIMEM Prototype system (Sockets over UNIMEM)

#### 3.1.6 FPGA Prototype System

The Exanode System drags it compute performance out of Field-Programmable-Gate-Arrays (FPGA) to be competitive with state-of-the-art architectures configured with e.g. GPUs or other Accelerators. We are currently in the phase of setting up a small test-system consisting of Xilinx Ultrascale+ FPGAs and ARM 64bit cores in one package. This platform will be used to implement a GPI-Interface that is able to offload compute kernels to the FPGA and to monitor the external program execution. We will also evaluate different development environments for these FPGA kernels to be able to select the best workflow that integrates optimal into the GPI Build-Environment.

## 3.2 MPI

BSC has proposed to the Consortium that the high-level architectural design of the MPI port over UNIMEM should lie on the recently-emerged OpenFabrics Interfaces (OFI)<sup>2</sup>, an open generic low-level networking standard for HPC. This is in accordance with current efforts in the major MPI implementations (Intel MPI, MPICH, Open MPI). The effort is performed to overcome the well-known performance limitations of TCP, so we expect to improve upon an MPI over TCP implementation and, when finished, offer minimal overhead with respect to direct use of UNIMEM.

#### 3.2.1 State-of-the-Art MPICH

Currently MPICH, the MPI implementation decided to be the primary target in this project, is undergoing a major code rewriting on its Channel layer, moving from CH3 to the new CH4, with major improvements on scalability and latency. Part of this effort is aimed at better exploiting HPC networking capabilities, by providing full communication semantics to the lowlevel network interface. This enables highly efficient MPI communications on top of OFI. Currently in alpha 2 version and already passing most of the wide MPICH test suite on x64

<sup>&</sup>lt;sup>2</sup> https://ofiwg.github.io/libfabric

architectures, a stable release is foreseen to be announced in November 2017 during the SC17 conference.

#### 3.2.2 MPI over UNIMEM Architecture

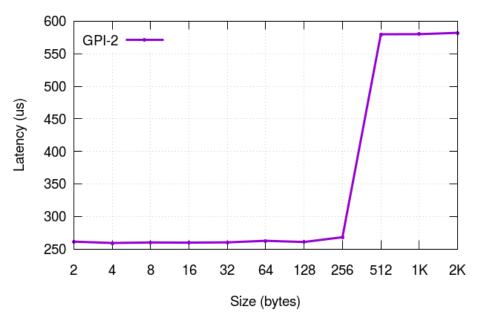

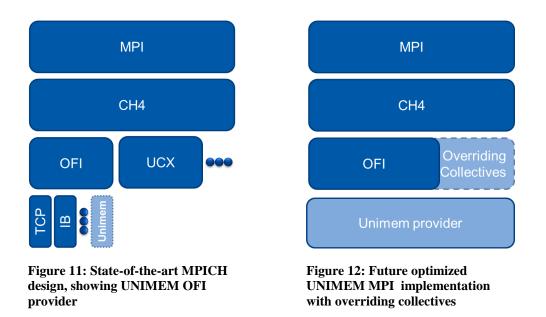

BSC is developing an OFI port (called a "provider") on top of the UNIMEM API. Figure 11 shows the major high-level architectural components of the state-of-the-art MPICH implementation described in the above section, and the light blue box represents the main component that BSC is developing: the UNIMEM OFI provider. Figure 12 depicts a future more optimised implementation of the UNIMEM version of MPI, with optimised collective communications that extend the OFI API. At this point there is no expectation of having to modify any layers of the MPI stack above OFI.

Developing an OFI provider instead of an integrated solution has the advantage that the UNIMEM OFI provider may be usable by other MPI implementations and potentially even other runtimes implementing the OFI API. BSC is currently targeting development under MPICH because of its current know-how and established contacts with the developing group, and the portability premise will be checked using Open MPI on a more advanced stage.

#### 3.2.3 Development Approach and Current Status

For practical reasons, rather than starting the implementation of the UNIMEM OFI provider from scratch, BSC chose to start development based on the OFI TCP/sockets provider, and progressively replace TCP/sockets communication with communication over the native UNIMEM API. This allows incremental development, with full functionality always provided by TCP/sockets, while taking advantage of improved performance for the features that have been optimized natively over the UNIMEM API.

Currently the OFI provider is able to transfer MPI\_Send data payloads over native UNIMEM. Discussions between BSC and FORTH resulted in improvements to the UNIMEM API, which will benefit MPI and the other runtimes/communication libraries: