European Exascale Processor & Memory Node Design

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 671578

# 3D-IC design solutions for modular integration of chiplet over silicon interposer

Pierre-Yves Martinez, <u>Denis Dutoit</u> CEA-LETI January 23<sup>rd</sup> 2018

31.01.2018

HiPEAC workshop: Towards Exascale HPC: the ExaNoDe, ExaNeSt, EcoScale, and EuroEXA projects

# Outline

## Advanced Packaging Integration:

- Technologies

- European project landscape

- High Performance Computing case

- ExaNoDe Advanced Packaging Technologies

# • 3D Integrated Circuit Design Solutions:

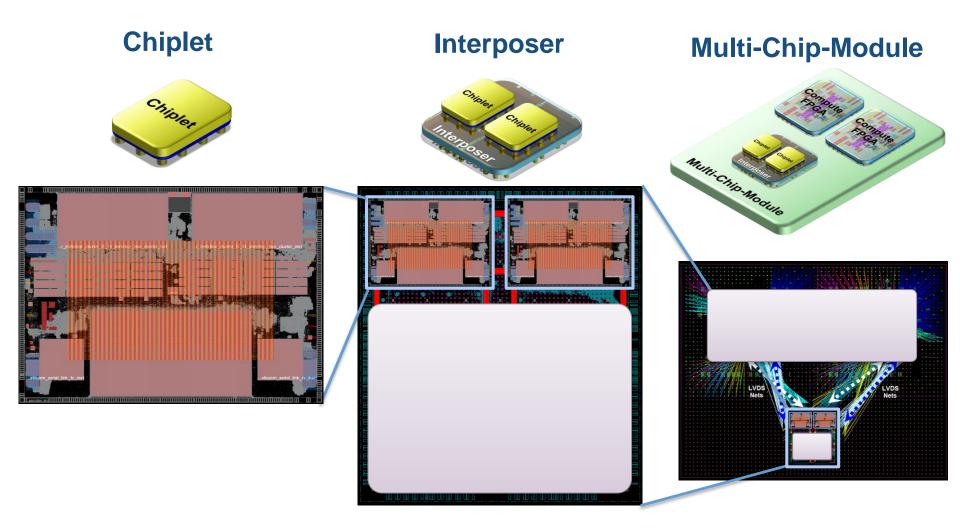

- ExaNoDe prototype assembly hierarchy

- Chiplet Architecture & Design

- Chiplet over Interposer Integration

# Multi-Chip-Module Challenges and Solutions:

- Placement and Routing

- Assembly Process

# Conclusion

# **Advanced Packaging Integration**

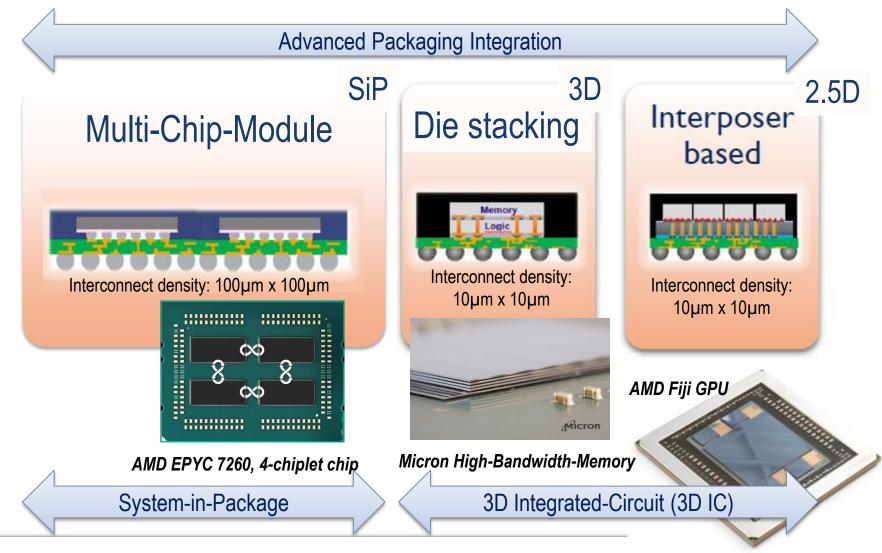

# Advanced Packaging Integration: Technologies

31.01.2018

Copyright © 2018 Members of the ExaNoDe Consortium

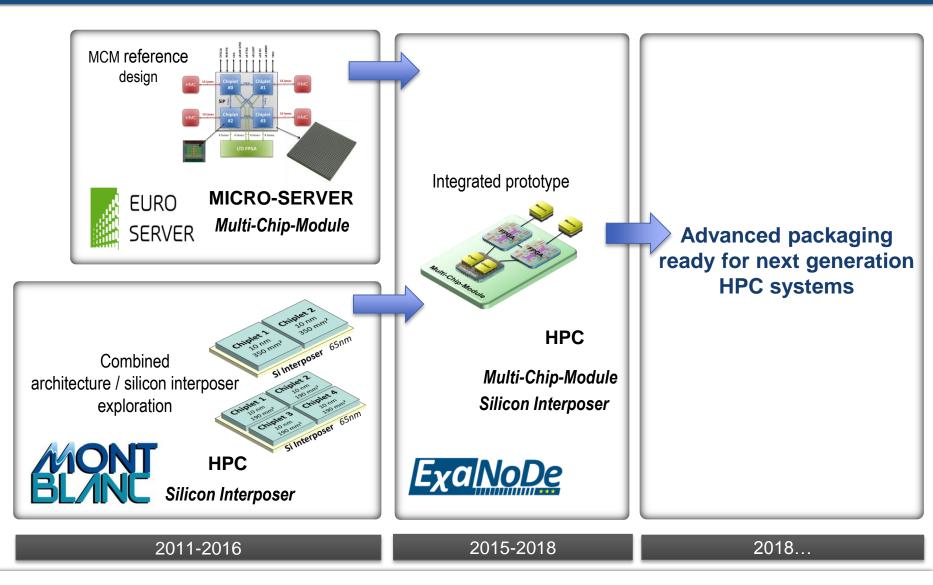

### Advanced Packaging among European HPC Projects

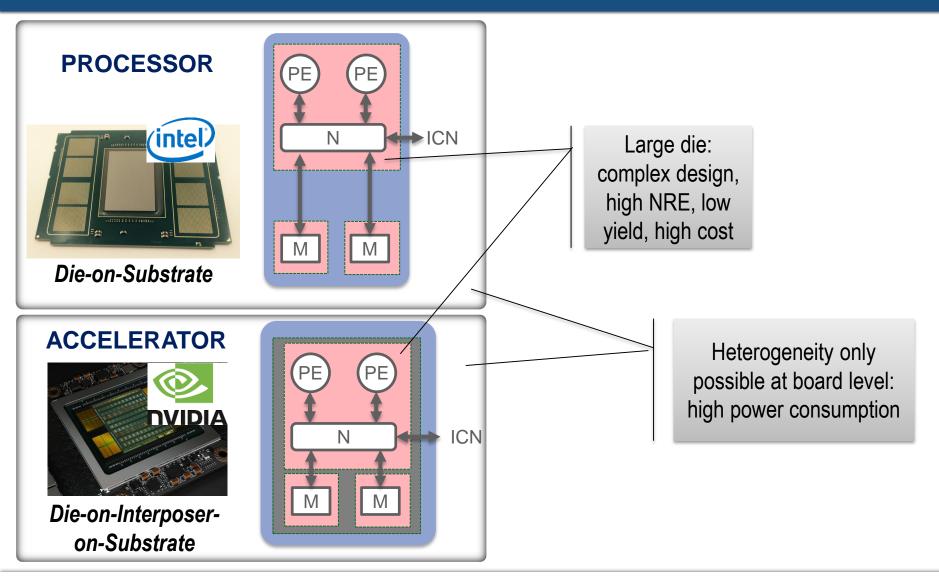

# Advanced Packaging Technologies for HPC

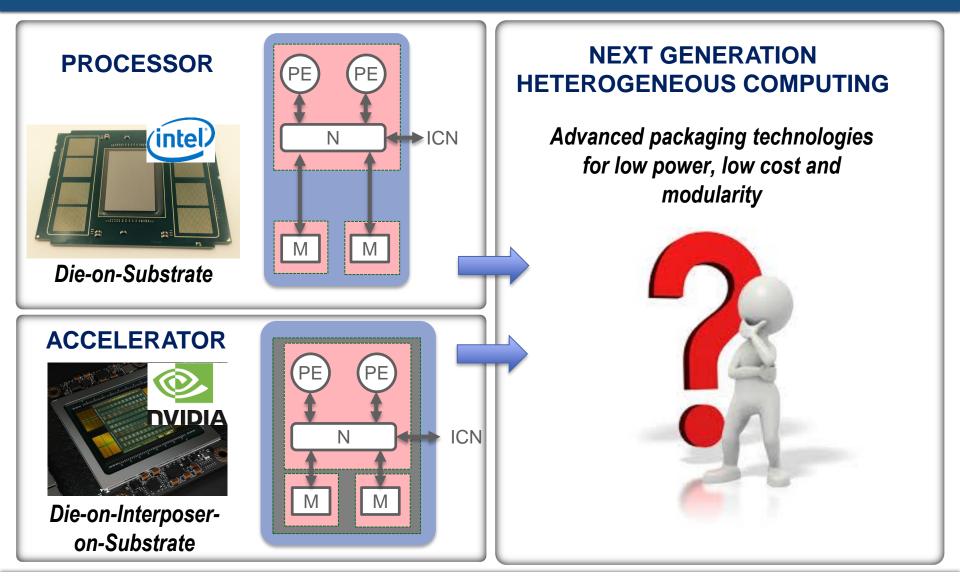

# Advanced Packaging Technologies for HPC

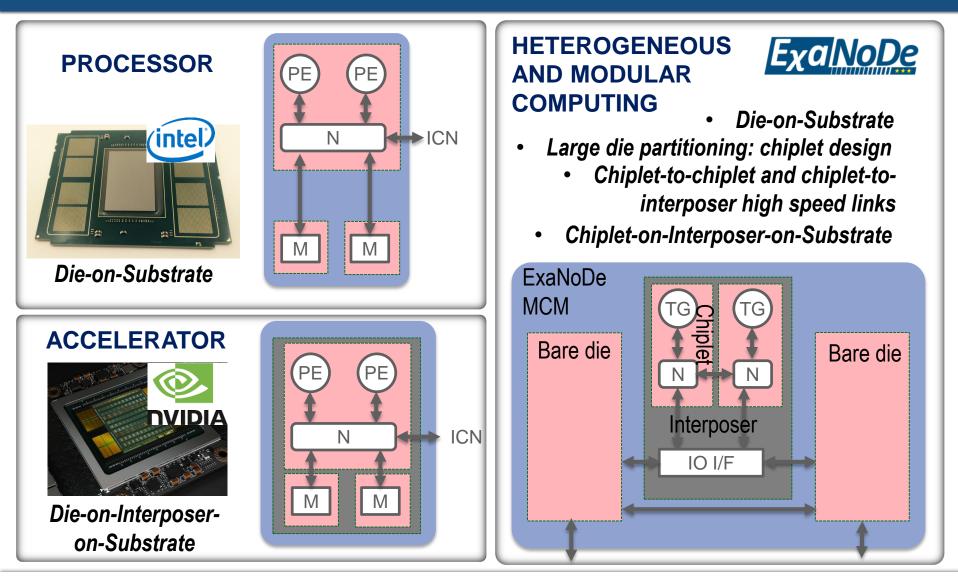

# ExaNoDe Advanced Packaging Technologies

# 3D Integrated Circuit Design Solutions

# ExaNoDe Assembly Hierarchy

31.01.2018

Copyright © 2018 Members of the ExaNoDe Consortium

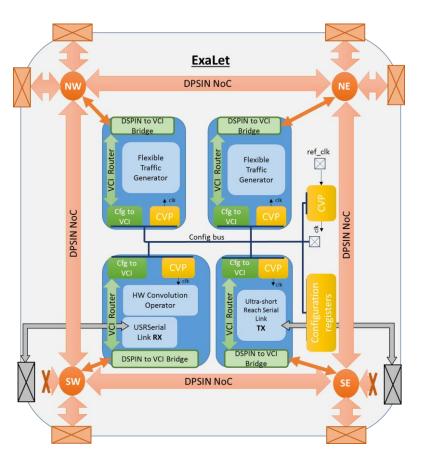

# **Chiplet Architecture**

31.01.2018

- Programmable Traffic generator (CEA)

- Ultra Short Reach chiplet-to-chiplet fast serial link (UOM)

- Mapping over the160 passive link available

- Convolutional Neural Networks (ETHZ)

- Bridge VCI <--> AXI (CEA/ETHZ)

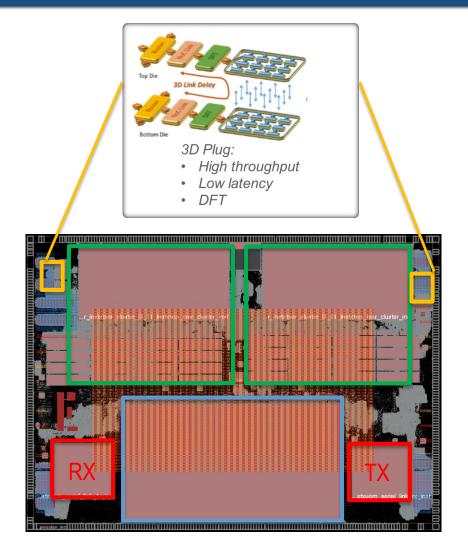

- DSPIN Network on chip and 3D plug (CEA)

- communication between clusters and inter-chiplet

FLL

# **Chiplet Design**

- 28FDSOI STM process

- Tape out on June 7<sup>th</sup>, 2017

- Timing closed over the full window of the process variation defined by the foundry

- Wafers back from fab end of 2017

- Ready for 3D bump growth steps

- Convolutional Neural Networks (ETHZ)

- Programmable Traffic generator (CEA)

- Ultra Short Reach chiplet to chiplet fast serial link (UOM)

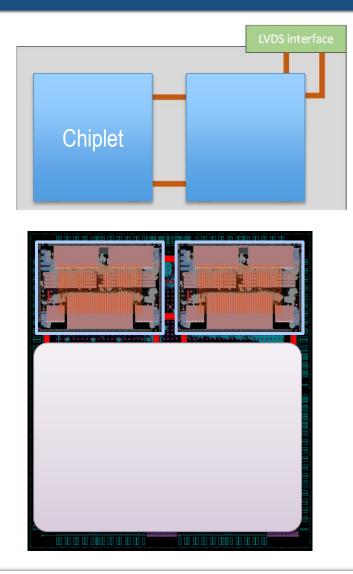

# **Chiplet over Interposer Integration**

#### • 3D Integrated Circuit:

- Chiplet design with communication infrastructure and HW accelerators.

- Interposer design with FPGA interface.

- Chiplet to chiplet high speed serial link communication

- Multi-level global interconnect

- Embedded DC-DC on the interposer for chiplet supply voltage adjustment

# Multi-Chip-Module Challenges and Solutions

# Multi-Chip-Module Challenges and Solutions

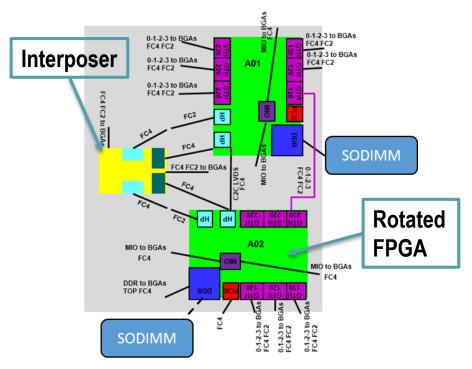

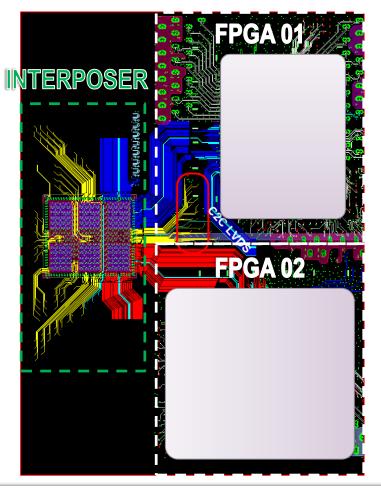

### MCM components positioning and routing

FPGA orientation and bank assignations optimized to reduce LVDS crossings and allow SODIMM connection (board level)

# Multi-Chip-Module Challenges and Solutions

## MCM assembly process

#### Stage 1

- Decoupling capacitors, FPGAs and interposer placement (pick & place, flip chip)

- Mass reflow

Module

#### Stage 2

Chiplets stacking on interposer by thermocompression bonding

#### Stage 3

31.01.2018

- Copper lid placement

- BGA placement and reflow

Copyright © 2018 Members of the ExaNoDe Consortium

Module

# Conclusion

#### Advanced Packaging:

• a key enabling technology for high performance and power efficient processors and accelerators.

#### ExaNoDe main innovations related to advanced packaging:

- 3D Integrated Circuit design solutions,

- Ultra Short Reach chiplet-to-chiplet fast serial link,

- 3D plug for chiplet-to-interposer wide data link,

- Chiplet-on-Interposer-on-MCM assembly process.

31.01.2018

#### ExaNoDe advanced packaging enables:

- modularity thanks to chiplet design solutions,

- power efficient heterogeneity with Chiplet-on-Interposer-on-MCM assembly process.

#### **Acknowledgements:**

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 671578

Part of this work was funded thanks to the French national program "Programme d'Investissements d'Avenir, IRT Nanoelec" ANR-10-AIRT-05

#### European Exascale Processor & Memory Node Design

www.exanode.eu