#### Future and Emerging Technologies (FET) TOWARDS EXASCALE HIGH PERFORMANCE COMPUTING

## EUROPEAN EXASCALE PROCESSOR MEMORY NODE DESIGN

# AFFORDABILITY EVERYTHING CLOSE POWER EFFICIENCY

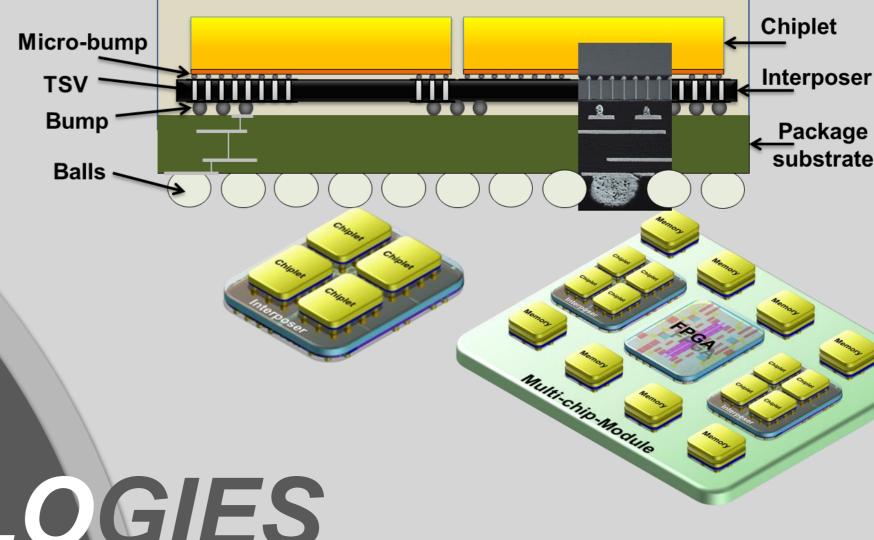

## INTEGRATION **TECHNOLOGIES**

- Chiplet on active interposer integration

- Multi-chip-Modules

ARCHITECTURE

ARMv8 processors

Scale-out architecture

## 7 I i Zürich

Fraunhofer

**ARM**

Coordinator

Cea

Supercomputing

The University of Manchester

VISION

CORE TECHNOLOGIES

ExaloDe

web: www.exanode.eu

### PROJECT OUTLINE

**Project** European Exascale Processor Memory Node Design title Start October 1st, 2015 Duration 36 months Call ID H2020-FETHPC-2014 FETHPC-1-2014: HPC Core Topic Technologies, Programming Environments and Algorithms for Extreme Parallelism and **Extreme Data Applications** 8.6 M€ Budget

OBJECTIVES

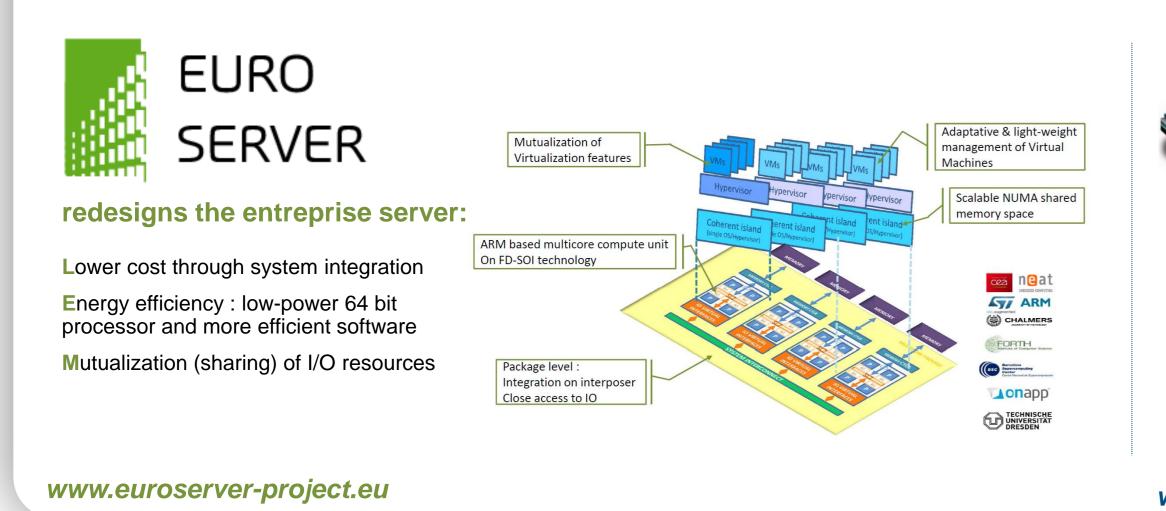

#### **Coherent island: Coherent island: Coherent island: Coherent island: ARMv8-A Cores ARMv8-A Cores ARMv8-A Cores ARMv8-A Cores** L1, L2, Coherent L1, L2, Coherent L1, L2, Coherent L1, L2, Coherent Interconnect Interconnect Interconnect **Interconnect** Multi-level Global Interconnect for coherent island communication Local & Coherent Local & Coherent Local & Coherent **Address Space Address Space Address Space Address Space** Memory scheme principles: UNIMEM 1. Each memory page can be cacheable to a single owner Shared I/O (coherent island) either locally or remotely but not both. 2. A processor (or DMA) can access any page in the system **Compute Node** through the page owners coherent interconnect. Compute Node example with 4 coherent islands **Inter-device bridging**

# EXANODE PROOF-OF-CONCEPT (POC)

- Deliver a compute node integrating core technologies consistent with the HPC system sizings and requirements for exascale computing.

- Validate the ExaNoDe core technologies as enablers for European exascale HPC in an appropriately balanced integrated PoC solution.

## SOFTWARE STACK:

- UNIMEM memory scheme

- Virtualization

Balanced **Mini-applications** Virtualization Parallel programming **OS**, Firmware Software Stack Module

## Example as part of a global strategy

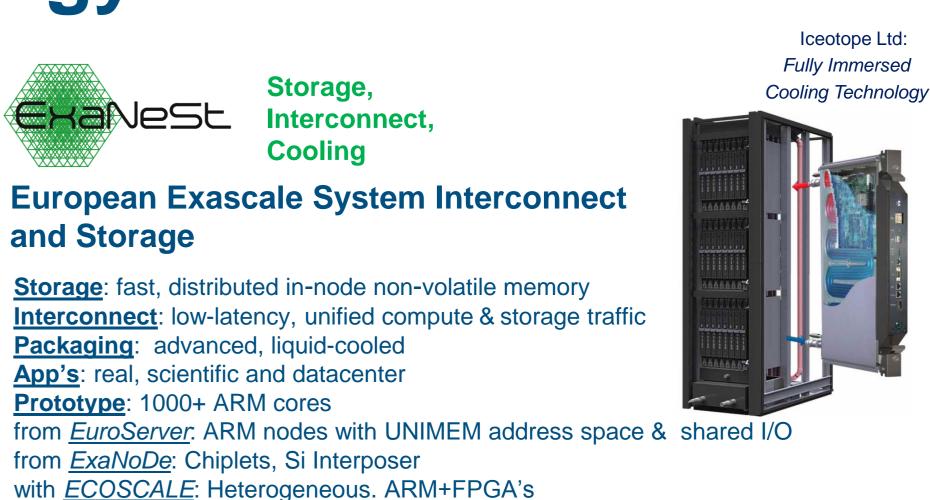

www.exanest.eu

Hardware